FPGA-Centric Design Concepts for Advanced Test and Measurement Systems

AmiES 2025

Peter Schulz

#### Context ATE

### Automatic Test Equipment

#### Content

- Motivation

- FPGA-based concepts

- Synthetic Instruments

- The Cyber Physical Test System (CPTS)

- Digital Twin of a Unit Under Test (UUT-DT)

- Digital Twin of Automatic Test Equipment (ATE-DT / ATE-on-Chip)

- Outlook

#### Motivation I

# Synthetic Instruments

- Measurement Instruments

- may become obsolete!

- are expensive!

- have limited functionality!

- Synthetic Instruments

- are versatile computing platforms combined with measurement signals

- can be configured to replace a class of measurement instruments

- can mimic original measurement instruments' behavior

- may be low-cost

# Motivation II Why FPGAs?

- Why use Field Programmable Gate Arrays (FPGAs) rather than software?

- Realtime

- Concurrency

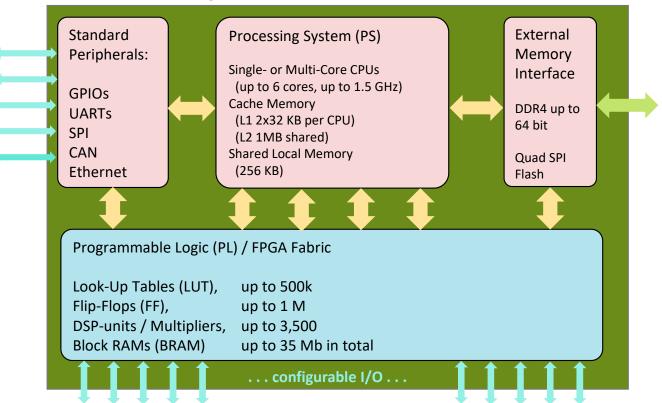

- System on Chip FPGA devices combine processing system (PS) with programmable logic (PL)

- capable of running SW and HW on one platform.

- Reconfigurability / Dynamic Function Exchange (DFX)

# Implementation Approach:

SoPC

- System on Programmable Chip (SoPC)

- the right platform for execution of logic circuits, DSP algorithms and software on a single chip (plus external memory, if needed)

## FPGA-based Synthetic Instruments

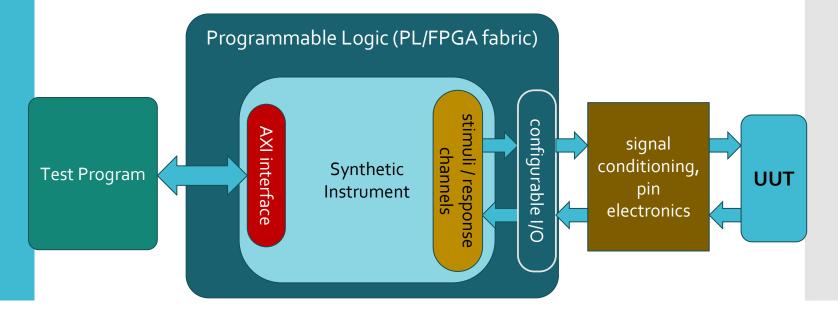

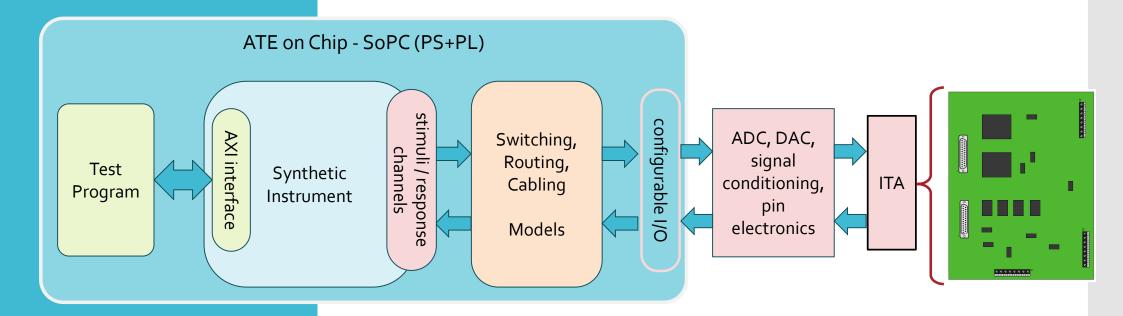

#### FPGA-based Synthetic Instrument

- FPGA-implemented VHDL or SystemVerilog model

- provides a register interface for control/status and data exchange (AXI)

- requires external physical layer for UUT-access (ITA, pin electronics)

- more signals possible if required (Trigger, Synchronization, etc.)

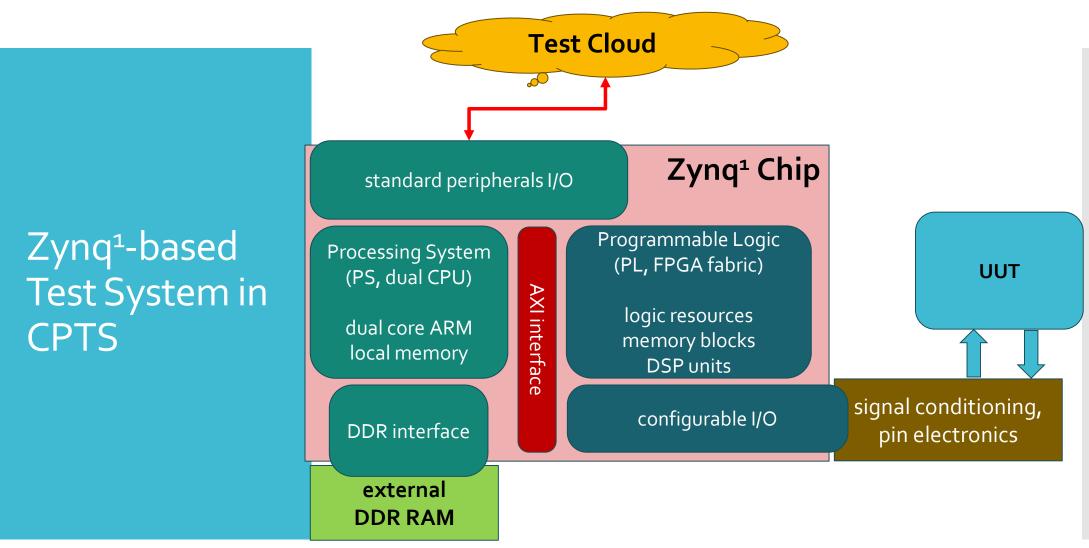

## **CPTS**

Low-Cost Test System with Cloud Connectivity

<sup>1</sup>Zynq is a trademark of AMD (Xilinx)

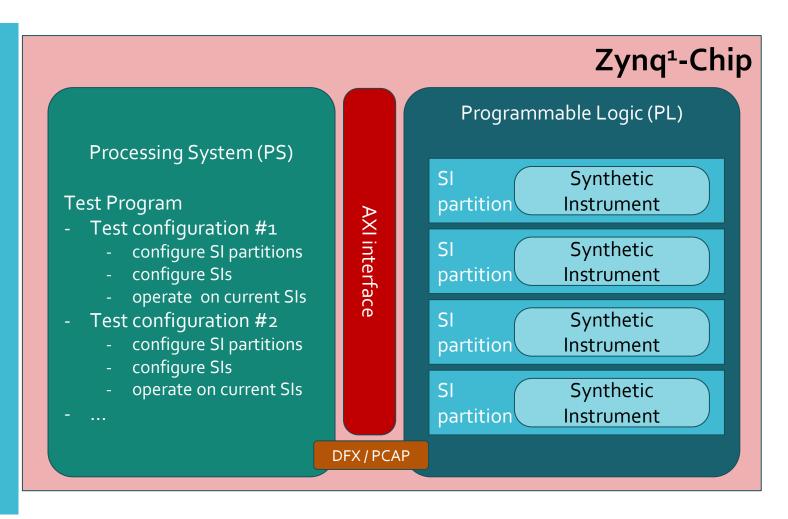

Allocation of Tasks in a Zynq-based Test System

<sup>1</sup>Zynq is a trademark of AMD (Xilinx)

# SI and *DFX* and *PYNQ*

- DFX: Runtime Hardware Reconfiguration

- Selective reconfiguration of FPGA Regions

- Static + Reconfigurable Partitions (RPs)

- Multiple Reconfigurable Modules (RMs)

- DFX features

- · No system shutdown required.

- · Results in Runtime functionality switching

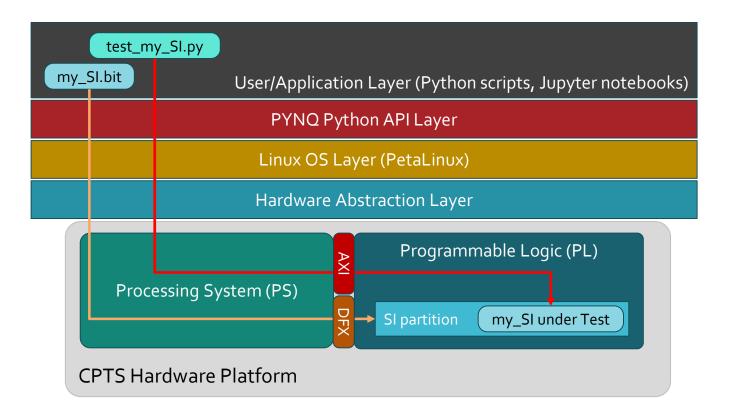

- Partial Reconfiguration Support with PYNQ

- PYNQ: "Python Productivity for Zynq"

- Rapid Prototyping: Python APIs for DFX integrated with a Jupyter notebook

- Increased Focus on Pipeline/Application development: Overlay-based HW abstraction for RM Management.

- Max System uptime : Runtime Bitstream Loading

- Overlay concept eases handling of Linux device driver for FPGA support.

#### SI management via PYNQ

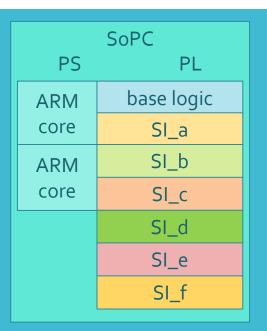

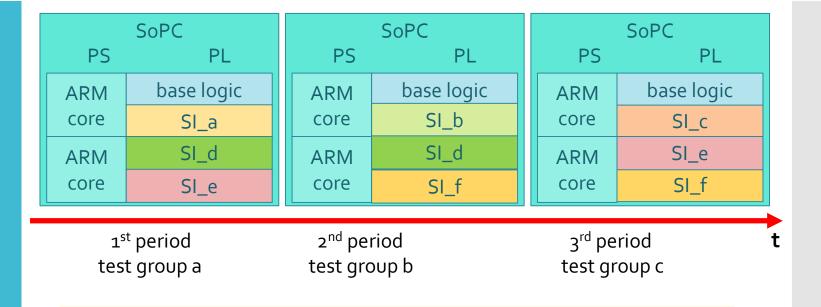

Hardware Multitasking

- <u>on the left:</u> static PL configuration with all synthetic instruments loaded permanently into a *big* PL

- on the right: smaller PL, partly reconfigured (DFX)

- Intermediate reconfigurations from test group to test group

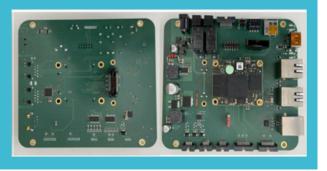

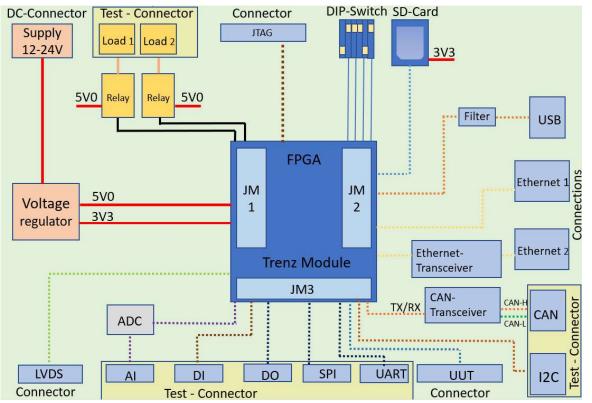

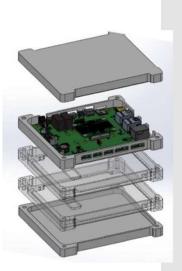

# CPTS Hardware Development

#### Main Unit

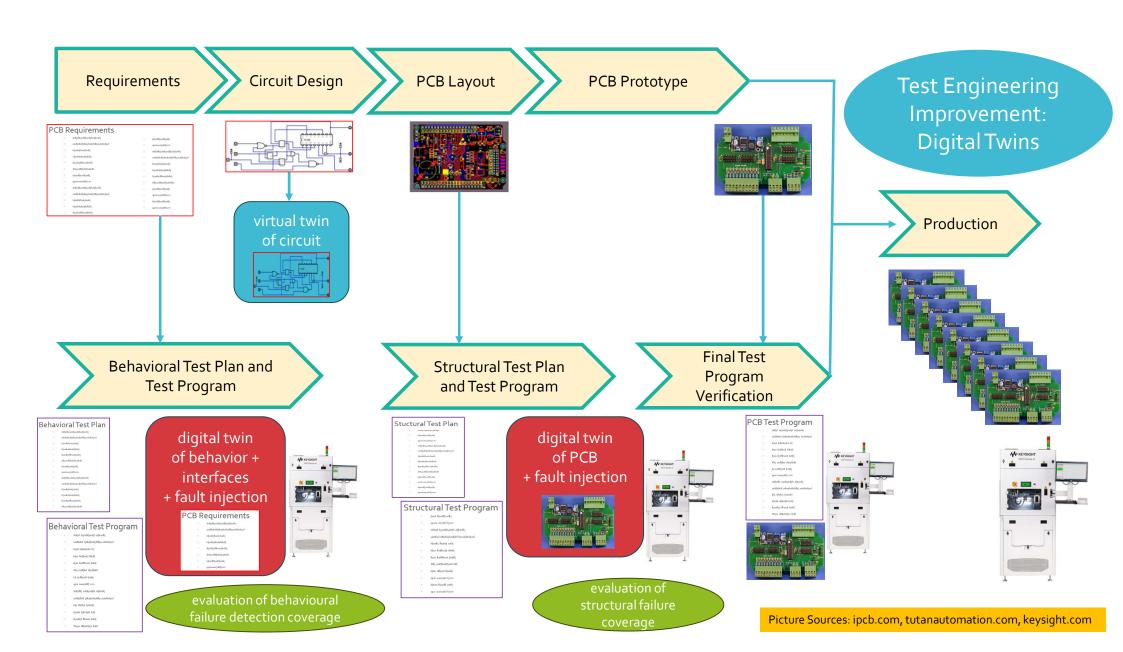

## **UUT-DT**

mimicking a Unit under Test

#### Motivation

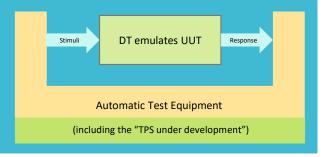

- An Automatic Test System (ATS) shall find nearly all detectable faults of a unit under test (UUT) by means of an end-to-end test.

- The ATS should also support diagnosing to the root cause by fault isolation.

- A Digital Twin (DT) that simulates a UUT can support development of the Test Program Set (TPS).

- Software implemented DTs are usual today but lack real-time behavior for UUTs of higher complexity.

- Field Programmable Gate Arrays (FPGAs) offer a reasonable approach to implement "real-time-DTs".

- Both approaches are reconfigurable and therefore can easily provide fault injection for TPS verification.

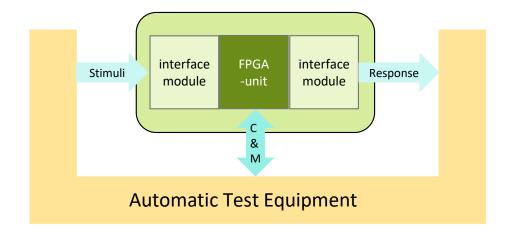

# FPGA-based DT concept

- UUTs are typically not purely digital assemblies. Therefore, the FPGA unit must be complemented with specific interface modules.

- When the ATE loads a new test suite, the DT may also need to be reconfigured via a Configuration & Management Interface (C&M).

### Technical Approach

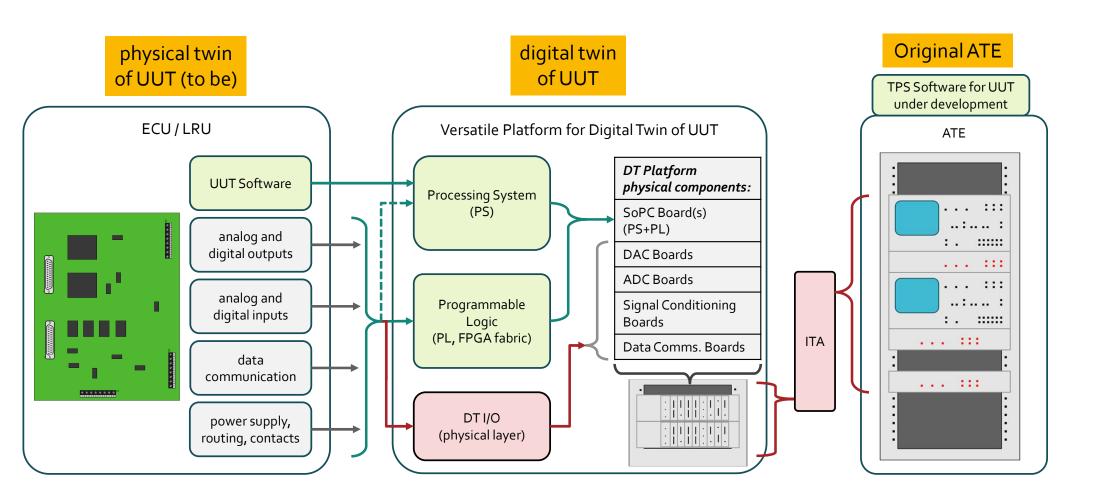

### UUT mimicking

#### **UUT** functional categories

- passive and analog electronic circuits

- digital circuits

- embedded software

#### How to mimic by FPGA-based DT?

- ADC and DAC interfaces as well as digitally emulated analog circuits using DSP principles (FPGA or software)

- FPGA directly executes the same logical behavior

- a processor that executes a compatible software

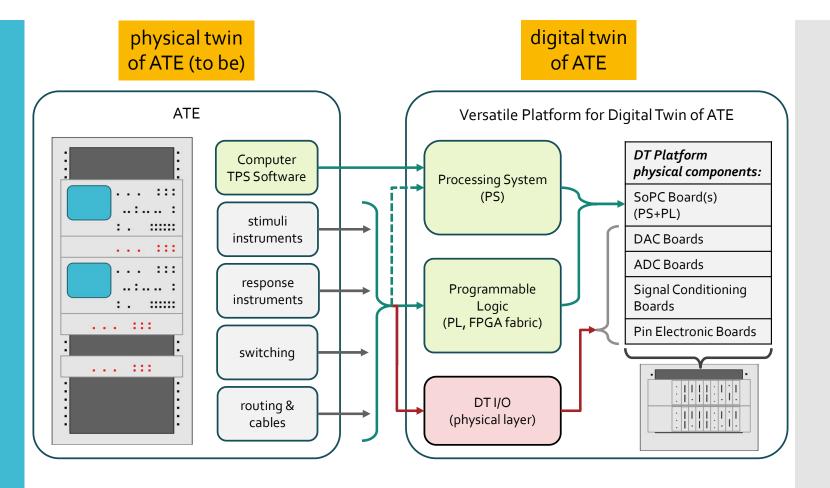

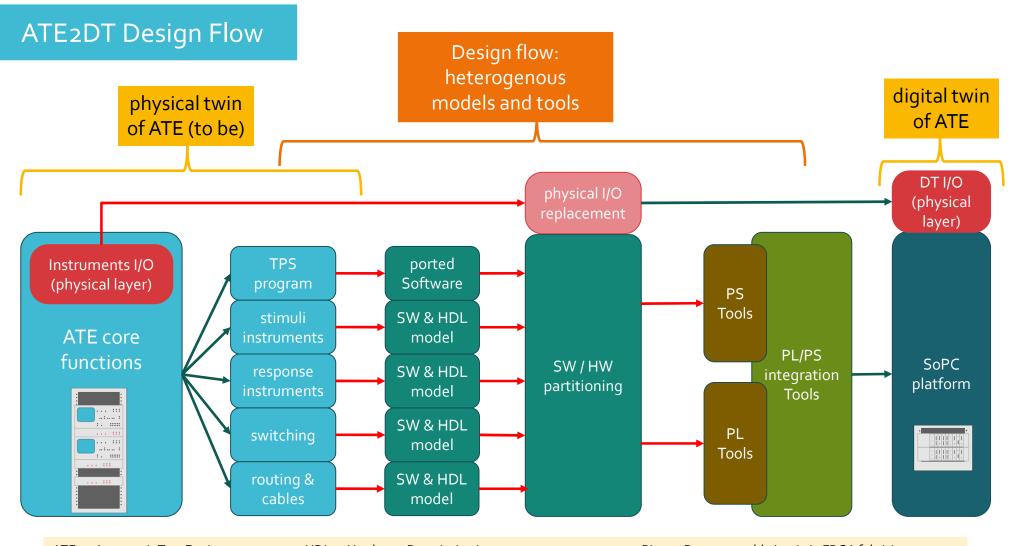

## ATE-DT

A Digital Twin of an ATE

#### Motivation

- A starting point for evaluating the requirements for (a yet to be designed) ATE

- Example: Replacing a legacy ATE with a new one that can run all TPSs already developed

- A tool for developing and debugging TPS

- ATE predictive maintenance

- Alerts need for calibration

- An indicator for remaining useful life of ATE

- A tool to find root causes in some instances of NFF

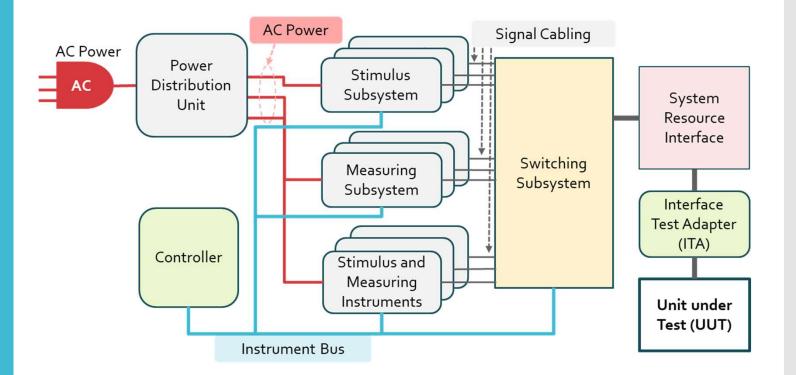

#### DT architecture

- Goal: Create a template which can be used for any ATE to be twinned.

- A combination from SW and FPGA Hardware

- customizable through different subsystems

- Subsystems DTs

- Instruments DTs (including model for calibration need)

- Measurement Instruments

- Stimulus Instruments

- Stimulus & Measurement Instruments

- Switching DT (including model of aging and wear out)

- Routing and cabling (including delays, bandwidth, attenuation)

- The same considerations as for the UUT-DT lead to the realization that FPGAs can form a suitable implementation platform.

- Can we implement a complete ATE DT using a single FPGA?

Physical Twin and Digital Twin of an ATE transformation

#### ATE-on-Chip

## Outlook

Digital Twin Design Flow is a Challenge!

ATE: Automatic Test Equipment PS: Processing System

HDL: Hardware Description Language

SoPC: System on Programmable Chip (= PS+PL)

PL: Programmable Logic (= FPGA fabric)

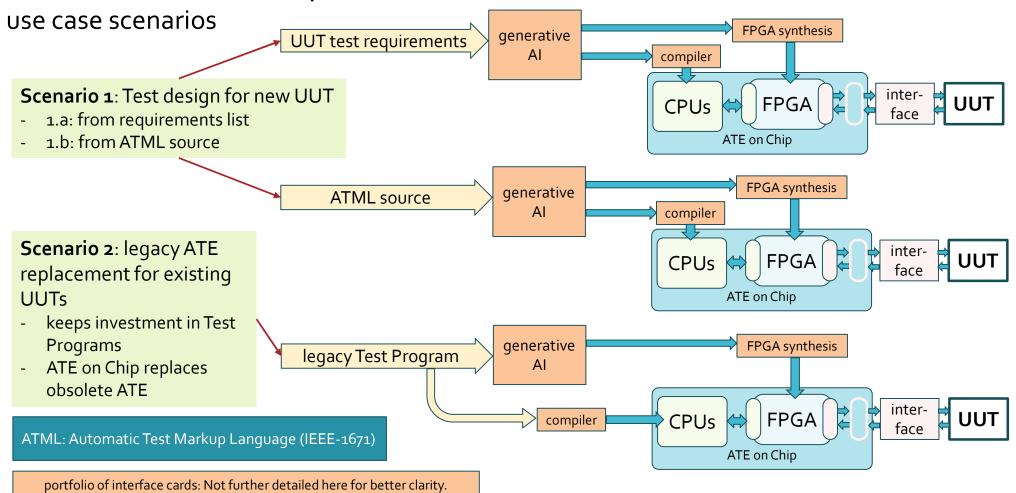

#### ITEA 2025 consortium of ai4idea2metal

- use case: "ATE on Chip"

# Thank you very much for your attention!

We have some time for discussion.